使用ULN振荡器的PLL

使用ULN振荡器的PLL

大多数石英晶体振荡器提共机械锁相和电调谐装置,以调节相位锁定或调制的频率或补偿长期漂移,机械调谐通常通过石英晶体电路中的微调电容器或者电感器来实现,该电容器或电感器通过振荡器外壳中的孔进入,机械锁相调谐在内部通过连接到基准电压的精密电位计完成,高质量微调电位器的机械稳定性超过了俱佳精密微调电容器的稳定性,使得在没有输入的情况下,振荡器恢复到电调谐的中点.

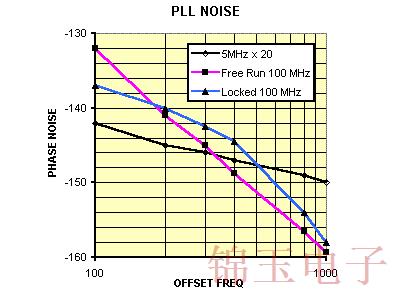

锁相两个超低噪声振荡器是一种有效的方法,可以在近距离和低噪声环境中实现出色的噪声性能,为了说明该技术,本说明描述了使用5MHzULN作为参考并使用100MHzULN作为锁定有源晶振的PLL,对于低于约300Hz的偏移频率,5MHz参考电压即使在乘法后也表现出优异的相位噪声,对于300Hz以上的偏移,100MHz振荡器具有更好的噪声,通过将环路带宽设置在300Hz附近,可以优化锁定的100MHz相位噪声.

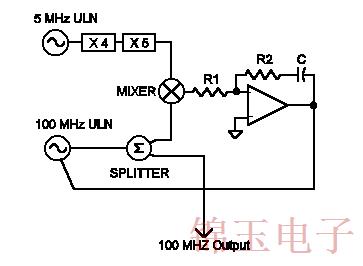

框图如下所示,5MHz振荡器乘以高达100MHz,而不是将100MHz振荡器降低到5 MHz,以避免陷入噪声基底限制:100MHz低抖动晶振的最低值接近-180dBc,除以20之后,理论噪声将206dBc,远低于任何分频器,混频器等的本底噪声,倍频器为ax4,LNHQ和x5,LNOM,此倍频器链仅在环路带宽以上的频率下略微降低5MHzULN,PLL电路包含在LNPLL的锁相模块中系列由肖特基二极管双平衡相位检测器组成,灵敏度约为伏弧度,接着是低噪声有损积分器,方框图中未显示低通滤波器,由1uH扼流圈和连接在混频器和R1之间的1uF电容组成,此滤波器的时间常数远高于环路带宽,并且不会显着影响环路.

低相噪振荡器的调谐灵敏度约为250Hz/V,约为1600rad/sec-volt,C选择为0.2uF,这将为R1提供相当低的值,这有助于降低PLL增加的噪声,这种2型PLL的带宽可以通过以下公式计算:

所需的300Hz带宽为1900弧度秒,对于上述等式中的R1,其值为2.2k,环路阻尼由R2设置,并调整到相当高,以减少谐振时的噪声峰值,值为15k时阻尼系数接近3.对于远低于300Hz的频率,锁定的100MHz振荡器紧密跟随乘以5MHz石英振荡器的噪声,对于远高于300Hz带宽的频率,锁定振荡器的噪声接近其自由-运行值,仅通过功率分配器的效果降低,下图显示了转换发生时100和1kHz之间频率的噪声,请注意,噪声比噪声曲线交叉的两个自激振荡器差大约3dB.

PLL设计非常简单,但必须注意几个细节才能获得最佳噪声性能,如果将大量过量噪吉施加到调谐输入,则锁定振荡器的噪声将降低,可以通过在锁定环路时将音频分析仪连接到运算放大器输出来测量此噪声,观察到的噪声可能是好的,因为它可能是将锁定振荡器的频谱清除到环路带宽以下所需的校正信号,但对于高于环路带宽的频率,这种噪声可能是过量的,也就是说,它可能是由于组件噪音,可以避免,要确定观察到的噪声是否可能是锁定相位噪声频谱的原因,请计算测量噪声(如果是随机噪声)可能产生的相位噪声.

如果振荡器比电平好得多,则噪声可能是由于噪声过大造成的,但是如果接近环路带宽将导致环路不稳定,通常需要使用其他降噪技术,使用相当低值的电阻器,以避免将运算放大器噪声电流转换为显着的噪声电压,如果电源经过良好滤波且输入波形良好,则交流逻辑可以很好地工作适当调节,避免对电压控制振荡器进行分频,因为大多数分频器不能支持更好的振荡器的噪声,最后,确保将振荡器连接到混频器的机制不会增加明显的噪音.

收藏本站

收藏本站 网站地图

网站地图 联系锦玉

联系锦玉

扫一扫

扫一扫